# CHAPTER 1

# **COMBINATIONAL LOGIC**

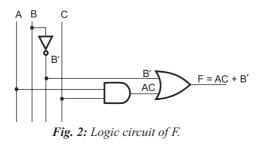

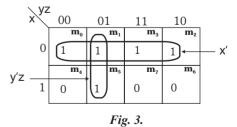

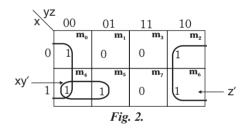

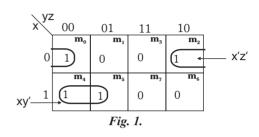

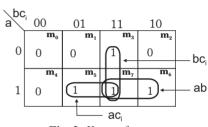

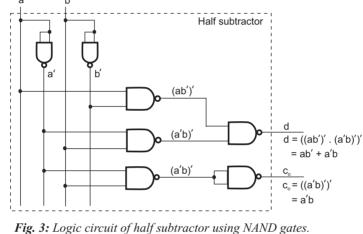

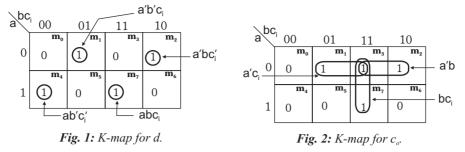

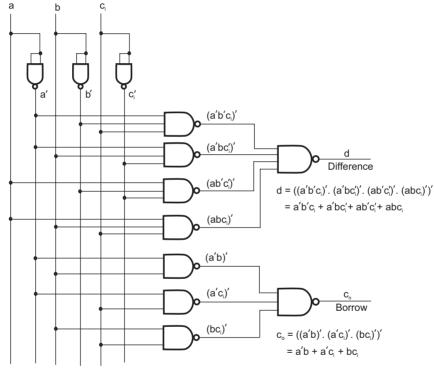

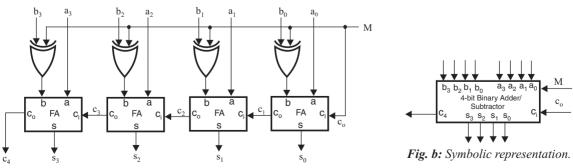

# **1.1 Introduction to Combinational Circuits**

Electronic circuits constructed using digital logic gates and devices and designed to operate on digital inputs and outputs are called *digital logic circuits*. The digital logic circuits can be broadly classified into combinational circuits and sequential circuits.

The combinational circuits are digital logic circuits without feedbacks from output to input. Therefore, the outputs of combinational circuit will depend only on present inputs.

*Fig. 1.1:* Block diagram representation of a combinational circuit.

The sequential circuits are digital logic circuits with feedback from output to input, the sequential circuits are discussed in Chapter-2.

The combinational logic does not depend on feedback signals or previous output. The logical operations are performed using present inputs. The circuits that perform combinational logic operations are called *combinational logic circuits* and they are constructed using logic gates. The working of logic gates are governed by Boolean algebra and hence the design of combinational circuits requires a knowledge about Boolean algebra.

In combinational circuits the output at any time depends on input at that time. In combinational circuits there is no storage element and there is no feedback from output to input. Therefore, combinational circuits are designed for applications which do not require a record of previous outputs and for applications in which the present outputs do not depend on previous outputs. Some examples of combinational circuits are shown in Fig. 1.2.

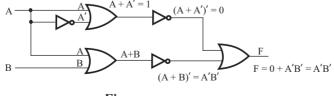

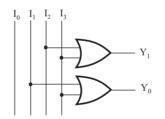

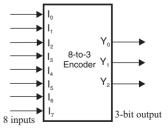

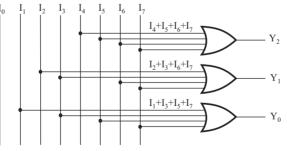

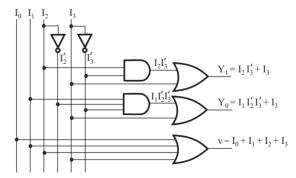

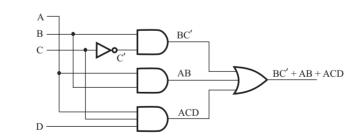

Fig. a.

Fig. 1.2: Examples of combinational circuit.

# 1.1.1 Problem Formulation and Design of Combinational Circuits

The combinational circuits are designed to provide hardware based solution for logical problems. The design starts with problem specifications. The procedure to design a combinational circuit is given below:

- 1. Determine the required inputs and outputs from the problem specifications.

- 2. Assign a symbol to each input and output.

- 3. Derive the truth table.

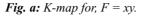

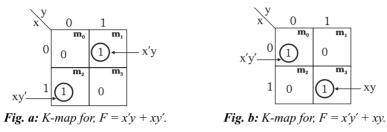

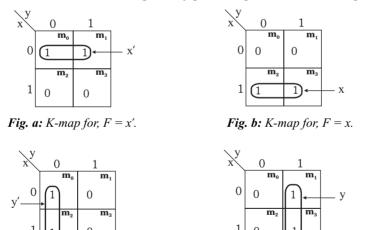

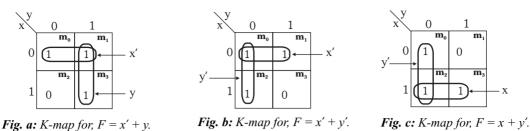

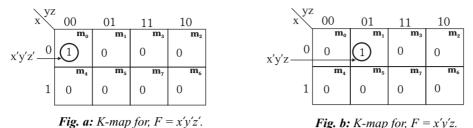

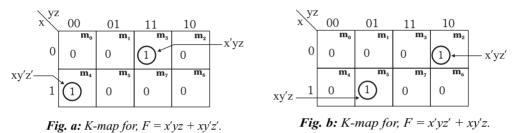

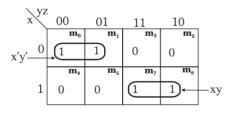

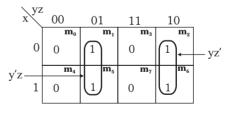

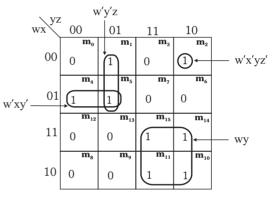

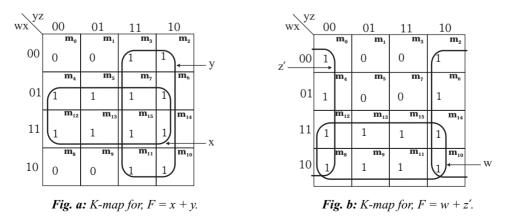

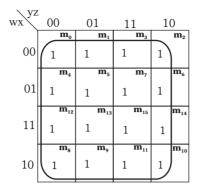

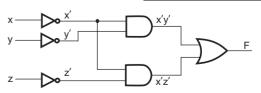

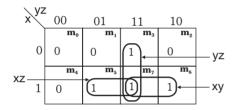

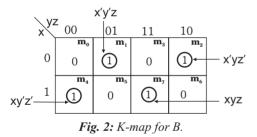

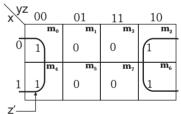

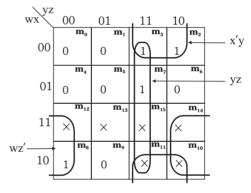

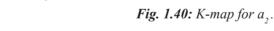

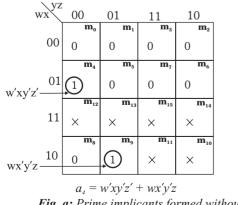

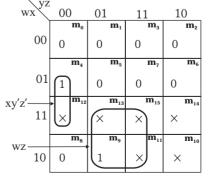

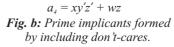

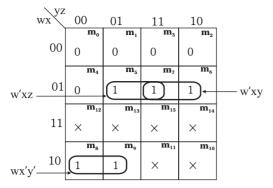

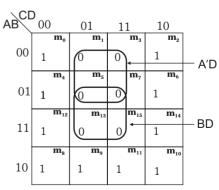

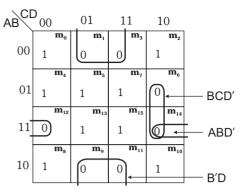

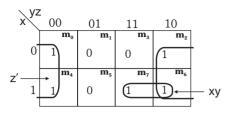

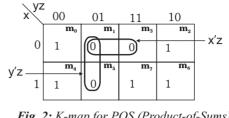

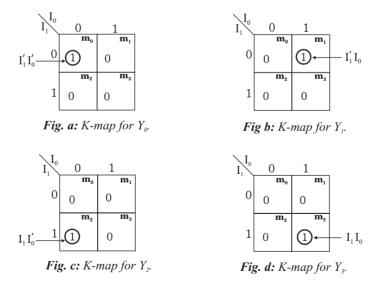

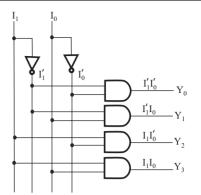

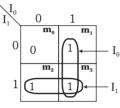

- 4. Draw K-map for every output and form the prime implicants.

- 5. Determine the simplified Boolean function for every output from the prime implicants.

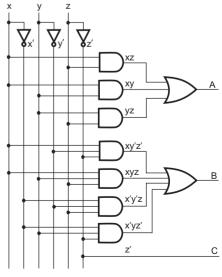

- 6. Implement the Boolean functions of all the outputs as a digital circuit using logic gates.

# 1.2 Boolean Algebra

George Boole developed Boolean algebra in 1854.

Boolean algebra is an algebraic structure that includes a set of elements consisting of

- Binary operators, " + " and " . "

- Binary variables, x, y, z .....

- Binary elements, 0 and 1

- Boolean postulates and theorems

Let x and y be two boolean variables that can take all possible combination of binary value. The rules for binary operators " + " and " . " are listed in Table 1.1 using the two binary variables x and y.

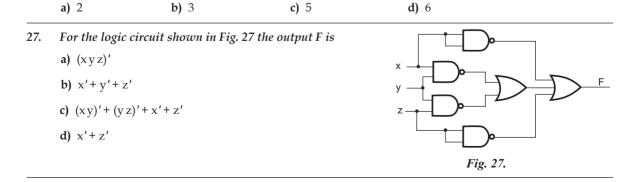

#### Table 1.1: Rules for Binary Operators "+" and "."

| X | у | <b>x . y</b> | x + y | x | x' |

|---|---|--------------|-------|---|----|

| 0 | 0 | 0            | 0     | 0 | 1  |

| 0 | 1 | 0            | 1     | 1 | 0  |

| 1 | 0 | 0            | 1     |   |    |

| 1 | 1 | 1            | 1     |   |    |

## **Operator Precedence while Evaluating Boolean Expression**

A statement written with Boolean variables, constants and operators is called *Boolean expression*. Examples of Boolean expression:  $x + y \cdot z'$

$$(x \cdot y) + z' + (x + y \cdot z)'$$

In order to evaluate Boolean expression the operator precedence is as follows:

Step-1: Evaluate expression with in paranthesis, i.e, within ().

Step-2: Evaluate complement

Step-3: Evaluate "."

Step-4: Evaluate " + "

*Note:* To simplify Boolean expression dot operation is represented without operator.

$x \cdot y \Rightarrow xy$   $y \cdot z \Rightarrow yz$   $x \cdot y \cdot z \Rightarrow xyz$

#### Example 1.1

Demonstrate the operator precedence in the evaluation of following Boolean expression.

**a)**  $x + y \cdot z'$  **b)**  $(x \cdot y) + z' + (x + y \cdot z)'$

#### Solution

```

a) \mathbf{x} + \mathbf{y} \cdot \mathbf{z}'

x + \mathbf{y} \cdot \mathbf{z}'

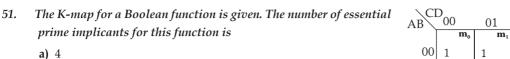

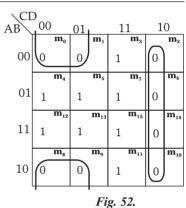

\downarrow

\downarrow

\mathbf{y} \cdot \mathbf{z}' First stage

\downarrow

\mathbf{y} \cdot \mathbf{z}' Second stage

\downarrow

\mathbf{x} + \mathbf{y} \cdot \mathbf{z}' Third stage

```

# 1.2.1 Duality

The *duality* principle of Boolean algebra states that every algebraic expression deducible from the postulates of Boolean algebra remains valid if the operator and identity element are interchanged. Here, the operators are " + " and " . " and the identity elements are " 0 " and " 1 ".

# Table 1.2: Basic Example of Duality

# **1.2.2 Postulates of Boolean Algebra**

Postulates of Boolean algebra are developed by E. V. Huntington in 1904.

Boolean structure have to satisfy the following postulates.

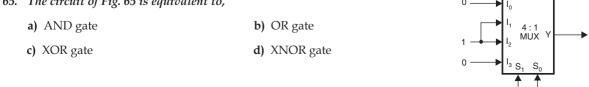

- 1. a) The structure is closed with the respect to operator " + "

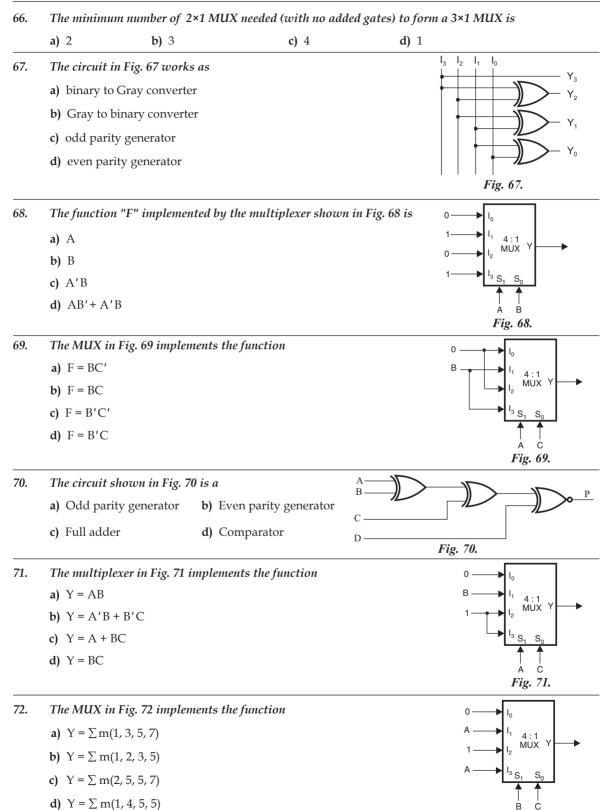

- **b**) The structure is closed with respect to operator "."

- 2. a) The element 0 is an identity element with respect to operator " + "

- $\therefore x + 0 = x$

$$0 + x = x$$

where x is a Boolean variable that can take a value either 0 or 1.

- b) The element 1 is an identity element with respect to operator "."

- $\therefore x \cdot 1 = x$

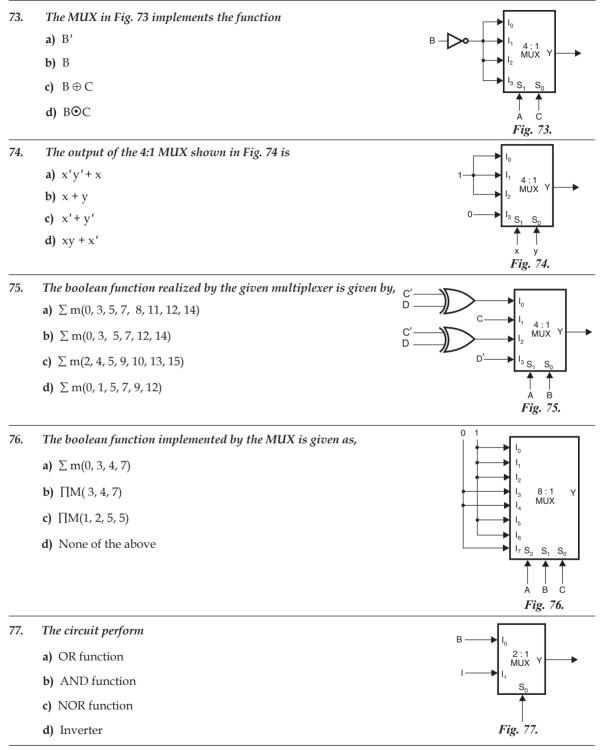

$1 \cdot x = x$

where x is Boolean variable that can take a value either 0 or 1.

- 3. a) The structure is commutative with respect to operator " + "

- $\therefore x + y = y + x$

where x and y are two Boolean variables.

- b) The structure is commutative with respect to operator "."

- $\therefore x \cdot y = y \cdot x$

- 4. a) The operator "." is distributive over operator "+"

$\therefore x . (y + z) = (x . y) + (x . z)$

**b)** The operator " + " is distributive over operator " . "

$\therefore x + (y \cdot z) = (x + y) \cdot (x + z)$

5. a) For every variable x there exists an element x' called complement of x

$\therefore x + x' = 1$  and  $x \cdot x' = 0$

6. There exists at least two variables x and y such that,  $x \neq y$ .

Distributive Law

## **Verification of Postulates**

1. From the Table 1.1 it is obvious that results of "+" and "." operations are either 0 or 1 and so structure is closed with respect to operators " + " and " . "

2. x + 0 = x, when x = 0, x + 0 = 0 + 0 = 0 = x x = 1, x + 0 = 1 + 0 = 1 = x 0 + x = x, when x = 0, 0 + x = 0 + 0 = 0 = x x = 1, 0 + x = 0 + 1 = 1 = x3.  $x \cdot 1 = x$ , when x = 0,  $x \cdot 1 = 0 \cdot 1 = 0 = x$  x = 1,  $x \cdot 1 = 1$ , 1 = 1 = x  $1 \cdot x = x$ , when x = 0,  $1 \cdot x = 1 \cdot 0 = 0 = x$ x = 1,  $1 \cdot x = 1 \cdot 1 = 1 = x$

**4.** Let x, y, z be three Boolean variables that takes all possible combinations of binary value. Construct a truth table for all possible combinations of x, y and z as shown in Table 1.3 to prove,

$$x \cdot (y + z) = (x \cdot y) + (x \cdot z)$$

| x | у | Z | y + z | $\mathbf{x} \cdot (\mathbf{y} + \mathbf{z})$ | <b>x</b> . y | x . z | $(\mathbf{x} \cdot \mathbf{y}) + (\mathbf{x} \cdot \mathbf{z})$ |

|---|---|---|-------|----------------------------------------------|--------------|-------|-----------------------------------------------------------------|

| 0 | 0 | 0 | 0     | 0                                            | 0            | 0     | 0                                                               |

| 0 | 0 | 1 | 1     | 0                                            | 0            | 0     | 0                                                               |

| 0 | 1 | 0 | 1     | 0                                            | 0            | 0     | 0                                                               |

| 0 | 1 | 1 | 1     | 0                                            | 0            | 0     | 0                                                               |

| 1 | 0 | 0 | 0     | 0                                            | 0            | 0     | 0                                                               |

| 1 | 0 | 1 | 1     | 1                                            | 0            | 1     | 1                                                               |

| 1 | 1 | 0 | 1     | 1                                            | 1            | 0     | 1                                                               |

| 1 | 1 | 1 | 1     | 1                                            | 1            | 1     | 1                                                               |

Similarly, Table 1.4 is constructed to prove,

$x + (y \cdot z) = (x + y) \cdot (x + z)$

Table 1.4: Verification of (Distributive Law)  $x + (y \cdot z) = (x + y) \cdot (x + z)$

| x | У | z | y . z | $\mathbf{x} + (\mathbf{y} \cdot \mathbf{z})$ | (x + y) | (x + z) | $(x+y) \cdot (x+z)$ |

|---|---|---|-------|----------------------------------------------|---------|---------|---------------------|

| 0 | 0 | 0 | 0     | 0                                            | 0       | 0       | 0                   |

| 0 | 0 | 1 | 0     | 0                                            | 0       | 1       | 0                   |

| 0 | 1 | 0 | 0     | 0                                            | 1       | 0       | 0                   |

| 0 | 1 | 1 | 1     | 1                                            | 1       | 1       | 1                   |

| 1 | 0 | 0 | 0     | 1                                            | 1       | 1       | 1                   |

| 1 | 0 | 1 | 0     | 1                                            | 1       | 1       | 1                   |

| 1 | 1 | 0 | 0     | 1                                            | 1       | 1       | 1                   |

| 1 | 1 | 1 | 1     | 1                                            | 1       | 1       | 1                   |

5. x + x' = 1when x = 0, x' = 1,  $\therefore x + x' = 0 + 1 = 1$ when x = 1, x' = 0,  $\therefore x + x' = 1 + 0 = 1$   $x \cdot x' = 0$ when x = 0, x' = 1,  $\therefore x \cdot x' = 0 \cdot 1 = 0$ when x = 1, x' = 0,  $\therefore x \cdot x' = 1 \cdot 0 = 0$

6. Boolean algebra has two elements 1 and 0, where  $1 \neq 0$ .

$\therefore$  If x and y are two variables, then there is a possibility that

$\begin{aligned} x &= 0, \ y = 1, \qquad \therefore \ x \neq y \\ \text{and} \ x &= 1, \ y = 0, \qquad \therefore \ x \neq y \end{aligned}$

## **1.2.3 Boolean Theorems**

| Theorem 1:                 | $\mathbf{x} + \mathbf{x} = \mathbf{x}$                                                                                                                  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | x . x = x                                                                                                                                               |

| Theorem 2:                 | x + 1 = 1                                                                                                                                               |

|                            | $\mathbf{x} \cdot 0 = 0$                                                                                                                                |

| Theorem 3:<br>(Involution) | $(\mathbf{x}')' = \mathbf{x}$                                                                                                                           |

| Theorem 4:                 | x + (y + z) = (x + y) + z                                                                                                                               |

| (Associative)              | $x \cdot (y \cdot z) = (x \cdot y) \cdot z$                                                                                                             |

| Theorem 5:                 | (x + y)' = x'. y'                                                                                                                                       |

| (DeMorgan's Law            | $(\mathbf{x} \cdot \mathbf{y})' = \mathbf{x}' + \mathbf{y}'$                                                                                            |

| or DeMorgan's<br>Theorem)  |                                                                                                                                                         |

| Theorem 6:                 | $\mathbf{x} + (\mathbf{x} \cdot \mathbf{y}) = \mathbf{x}$                                                                                               |

| (Absorption)               | $\mathbf{x} \cdot (\mathbf{x} + \mathbf{y}) = \mathbf{x}$                                                                                               |

|                            | (y is absorbed)                                                                                                                                         |

| Theorem 7:                 | $\mathbf{x} \cdot \mathbf{y} + \mathbf{x}' \cdot \mathbf{z} + \mathbf{y} \cdot \mathbf{z} = \mathbf{x} \cdot \mathbf{y} + \mathbf{x}' \cdot \mathbf{z}$ |

| (Consensus<br>Theorem)     | $(x + y) \cdot (x' + z) \cdot (y + z) = (x + y) \cdot (x' + z)$                                                                                         |

| Proof of Theorems                       |                                                 |

|-----------------------------------------|-------------------------------------------------|

| Theorem 1:                              | 1                                               |

| $\mathbf{x} + \mathbf{x} = \mathbf{x}$  | x . x = x                                       |

| when, $x = 0$ , $x + x = 0 + 0 = 0 = x$ | when, $x = 0$ , $x \cdot x = 0 \cdot 0 = 0 = x$ |

| when, $x = 1$ , $x + x = 1 + 1 = 1 = x$ | when, $x = 1$ , $x \cdot x = 1 \cdot 1 = 1 = x$ |

| Theorem 2:                              |                                                 |

| x + 1 = 1                               | x . 0 = 0                                       |

| when, $x = 0$ , $x + 1 = 0 + 1 = 1$     | when, $x = 0$ , $x \cdot 0 = 0 \cdot 0 = 0$     |

| when, $x = 1$ , $x + 1 = 1 + 1 = 1$     | when, $x = 1$ , $x \cdot 0 = 1 \cdot 0 = 0$     |

|                                         |                                                 |

## **Theorem 3: Involution**

$$(x')' = x$$

when, x = 0, (x')' = (0')' = 1' = 0 = xwhen, x = 1, (x')' = (1')' = 0' = 1 = x

# **Theorem 4: Associative**

x + (y + z) = (x + y) + zConstruct a truth table for all possible combinations of x, y and z as shown in Table 1.5 to prove,

x + (y + z) = (x + y) + z

$x \cdot (y \cdot z) = (x \cdot y) \cdot z$

Construct a truth table for all possible combinations of x, y and z as shown in Table 1.6 to prove,

$x \cdot (y \cdot z) = (x \cdot y) \cdot z$

Table 1.5: Verification of x + (y + z) = (x + y) + z

| X | у | Z | y + z | $\mathbf{x} + (\mathbf{y} + \mathbf{z})$ | x + y | (x+y)+z |

|---|---|---|-------|------------------------------------------|-------|---------|

| 0 | 0 | 0 | 0     | 0                                        | 0     | 0       |

| 0 | 0 | 1 | 1     | 1                                        | 0     | 1       |

| 0 | 1 | 0 | 1     | 1                                        | 1     | 1       |

| 0 | 1 | 1 | 1     | 1                                        | 1     | 1       |

| 1 | 0 | 0 | 0     | 1                                        | 1     | 1       |

| 1 | 0 | 1 | 1     | 1                                        | 1     | 1       |

| 1 | 1 | 0 | 1     | 1                                        | 1     | 1       |

| 1 | 1 | 1 | 1     | 1                                        | 1     | 1       |

Table 1.6: Verification of  $x \cdot (y \cdot z) = (x \cdot y) \cdot z$

| X | У | Z | y . z | x . (y . z) | <b>x</b> . y | (x . y) . z |

|---|---|---|-------|-------------|--------------|-------------|

| 0 | 0 | 0 | 0     | 0           | 0            | 0           |

| 0 | 0 | 1 | 0     | 0           | 0            | 0           |

| 0 | 1 | 0 | 0     | 0           | 0            | 0           |

| 0 | 1 | 1 | 1     | 0           | 0            | 0           |

| 1 | 0 | 0 | 0     | 0           | 0            | 0           |

| 1 | 0 | 1 | 0     | 0           | 0            | 0           |

| 1 | 1 | 0 | 0     | 0           | 1            | 0           |

| 1 | 1 | 1 | 1     | 1           | 1            | 1           |

## Theorem 5: DeMorgan's Theorem

$(x + y)' = x' \cdot y'$

Construct a truth table for all possible combinations of x and y as shown in Table 1.7 to prove,

$(x + y)' = x' \cdot y'$

Table 1.7: Verification of  $(x + y)' = x' \cdot y'$

| x | у | x + y | (x + y)' | x' | y' | x' . y' |

|---|---|-------|----------|----|----|---------|

| 0 | 0 | 0     | 1        | 1  | 1  | 1       |

| 0 | 1 | 1     | 0        | 1  | 0  | 0       |

| 1 | 0 | 1     | 0        | 0  | 1  | 0       |

| 1 | 1 | 1     | 0        | 0  | 0  | 0       |

## **Theorem 6: Absorption**

$$x + (x \cdot y) = x$$

Construct a truth table for all possible combinations of x and y as shown in Table 1.9 to prove,

$x + (x \cdot y) = x$

Table 1.9: Verification of  $x + (x \cdot y) = x$

| x | у | <b>x</b> . y | x + (x . y) |

|---|---|--------------|-------------|

| 0 | 0 | 0            | 0           |

| 0 | 1 | 0            | 0           |

| 1 | 0 | 0            | 1           |

| 1 | 1 | 1            | 1           |

## Theorem 7: Consensus Theorem

$x \cdot y + x' \cdot z + y \cdot z = x \cdot y + x' \cdot z$

Construct a truth table for all possible combinations of x, y and z as shown in Table 1.11 to prove,

$x \cdot y + x' \cdot z + y \cdot z = x \cdot y + x' \cdot z$

Table 1.11: Verification of  $x \cdot y + x' \cdot z + y \cdot z = x \cdot y + x' \cdot z$ v x'  $x \cdot y | x' \cdot z | y \cdot z | x \cdot y + x' \cdot z + y \cdot z | x \cdot y + x' \cdot z$ х Z

$(\mathbf{x} \cdot \mathbf{y})' = \mathbf{x}' + \mathbf{y}'$

Construct a truth table for all possible combinations of x and y as shown in Table 1.8 to prove,

$(\mathbf{x} \cdot \mathbf{y})' = \mathbf{x}' + \mathbf{y}'$

Table 1.8: Verification of  $(x \cdot y)' = x' + y'$

| X | у | х.у | ( <b>x</b> . <b>y</b> )' | <b>x</b> ′ | y' | $\mathbf{x'} + \mathbf{y'}$ |

|---|---|-----|--------------------------|------------|----|-----------------------------|

| 0 | 0 | 0   | 1                        | 1          | 1  | 1                           |

| 0 | 1 | 0   | 1                        | 1          | 0  | 1                           |

| 1 | 0 | 0   | 1                        | 0          | 1  | 1                           |

| 1 | 1 | 1   | 0                        | 0          | 0  | 0                           |

$x \cdot (x + y) = x$

Construct a truth table for all possible combinations of x and y as shown in Table 1.10 to prove,

$x \cdot (x + y) = x$

Table 1.10: Verification of  $x \cdot (x + y) = x$

| x | у | x + y | x . (x + y) |

|---|---|-------|-------------|

| 0 | 0 | 0     | 0           |

| 0 | 1 | 1     | 0           |

| 1 | 0 | 1     | 1           |

| 1 | 1 | 1     | 1           |

$$(x + y) \cdot (x' + z) \cdot (y + z) = (x + y) \cdot (x' + z)$$

Construct a truth table for all possible combinations of x, y and z as shown in Table 1.12 to prove,

$$(x + y) \cdot (x' + z) \cdot (y + z) = (x + y) \cdot (x' + z)$$

| Table 1.12: Verification of $(x + y) \cdot (x' + z) \cdot (y + z) = (x + y) \cdot (x' + z)$ |   |   |    |       |      |       |                                        |                          |

|---------------------------------------------------------------------------------------------|---|---|----|-------|------|-------|----------------------------------------|--------------------------|

| x                                                                                           | у | z | x' | x + y | x'+z | y + z | $(x + y) \cdot (x' + z) \cdot (y + z)$ | $(x + y) \cdot (x' + z)$ |

| 0                                                                                           | 0 | 0 | 1  | 0     | 1    | 0     | 0                                      | 0                        |

| 0                                                                                           | 0 | 1 | 1  | 0     | 1    | 1     | 0                                      | 0                        |

| 0                                                                                           | 1 | 0 | 1  | 1     | 1    | 1     | 1                                      | 1                        |

| 0                                                                                           | 1 | 1 | 1  | 1     | 1    | 1     | 1                                      | 1                        |

| 1                                                                                           | 0 | 0 | 0  | 1     | 0    | 0     | 0                                      | 0                        |

| 1                                                                                           | 0 | 1 | 0  | 1     | 1    | 1     | 1                                      | 1                        |

| 1                                                                                           | 1 | 0 | 0  | 1     | 0    | 1     | 0                                      | 0                        |

| 1                                                                                           | 1 | 1 | 0  | 1     | 1    | 1     | 1                                      | 1                        |

# **1.3 Binary Logic**

*Binary logic* consists of binary variables and a set of logical operations. The binary variables are denoted by letters of alphabet, A, B, C, ....., x, y, z, .....

Each binary variable can take only two possible values 0 or 1. In positive logic, 0 is **low** and 1 is **high**. The basic logical operations are AND, OR and NOT.

AND operation is same as "." operation. In positive logic, the logical AND of two or more variables will be 1 if and only if the value of all the variables is 1.

OR operation is same as " + " operation. In positive logic, the logical OR of two or more variables will be 1 if the value of any one of the variables is 1.

NOT operation is same as complement operation.

The results or outputs of logical operations of two or more variables for all possible combinations of the variables can be listed in a table called *truth table*. The truth tables of basic logical operations are shown in Table 1.13.

## Table 1.13: Truth Tables of AND, OR and NOT Operation of Two Variables

| ANI | AND operation |              | OR | ope | ration | NOT operat   | NOT operation |  |  |

|-----|---------------|--------------|----|-----|--------|--------------|---------------|--|--|

| x   | y             | <b>x</b> . y | x  | у   | x + y  | <b>x x</b> ' |               |  |  |

| 0   | 0             | 0            | 0  | 0   | 0      | 0 1          |               |  |  |

| 0   | 1             | 0            | 0  | 1   | 1      |              |               |  |  |

| 1   | 0             | 0            | 1  | 0   | 1      |              |               |  |  |

| 1   | 1             |              | 1  | 1   | 1      |              |               |  |  |

|     | -             |              |    |     |        |              |               |  |  |

# Positive and Negative Logic

Binary constants are 1 and 0. Physically in a digital circuit they represent two voltage levels. The two voltage levels are called **high** and **low**.

The voltage level of high and low depends on technology used to fabricate the gates.

In TTL logic (Transistor Transistor Logic) high is + 5 V and low is 0 V.

In CMOS (Complementry Symmetry MOSFET) high is +3.3 *V* and low is 0 *V*.

If, 1 represent high voltage and 0 represent low voltage then logic system is called *positive logic*.

If, 1 represent low voltage and 0 represent high voltage then the logic system is called *negative logic*.

| Logic Type        | Technology                      |                                    |  |  |

|-------------------|---------------------------------|------------------------------------|--|--|

| (or Logic System) | TTL                             | CMOS                               |  |  |

| Positive Logic    | 1 = High = +5 V $0 = Low = 0 V$ | 1 = High = +3.3 V<br>0 = Low = 0 V |  |  |

| Negative Logic    | 0 = High = +5 V $1 = Low = 0 V$ | 0 = High = +3.3 V<br>1 = Low = 0 V |  |  |

## **Table 1.14: Positive and Negative Logic Levels**

# **1.4 Logic Gates**

*Logic gates* are electronic devices or circuits that perform logical operations on one or more input logical variables and produce a binary output. The basic logic gates are AND, OR and NOT gates.

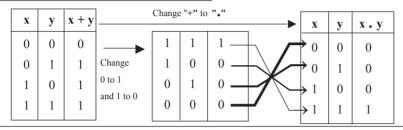

The logic gates have standard symbols as shown in Figs. 1.3 to 1.7.

## AND Gate

**AND** gate is an electronic device that performs logical AND operation of two or more variables.

Fig. 1.3: Two input AND gate. Fig. 1.4: Three input AND gate.

# **OR Gate**

**OR** gate is an electronic device that performs logical OR operation of two or more variables.

*Note: Theoretically, AND and OR gates can have any number of inputs.*

# **NOT Gate (or inverter)**

**NOT** gate is an electronic device that performs complement operation of a Boolean variable.

# Other Logical Operations

With n variables it is possible to form  $2^{2n}$  Boolean functions.

When, n = 2,  $2^{2n} = 2^{2 \times 2} = 2^4 = 16$

Therefore, with two variables we can form 16 Boolean functions.

All the 16 possible function of two variables are listed in Table 1.15.

The output of 16 functions are 16 binary combinations of 4-bit binary.

Let,  $F_0$ ,  $F_1$ ,  $F_2$ , ...,  $F_{15}$  be 16 possible Boolean functions for two variables x, y.

# Table 1.15: Two-Variable Boolean Functions

| Functions                                                       | X | у | F | Functions                                                       | X | у | F |

|-----------------------------------------------------------------|---|---|---|-----------------------------------------------------------------|---|---|---|

| Null operation                                                  | 0 | 0 | 0 | NOR operation                                                   | 0 | 0 | 1 |

| $F = F_0 = 0$                                                   | 0 | 1 | 0 | $F = F_8 = (x + y)'$                                            | 0 | 1 | 0 |

|                                                                 | 1 | 0 | 0 | 0                                                               | 1 | 0 | 0 |

|                                                                 | 1 | 1 | 0 |                                                                 | 1 | 1 | 0 |

| AND operation                                                   | 0 | 0 | 0 | Exclusive NOR(XNOR)                                             | 0 | 0 | 1 |

| $\mathbf{F} = \mathbf{F}_1 = \mathbf{x} \cdot \mathbf{y}$       | 0 | 1 | 0 | (or equivalence)                                                | 0 | 1 | 0 |

|                                                                 | 1 | 0 | 0 | $F = F_9 = x \odot y = (x \oplus y)'$                           | 1 | 0 | 0 |

|                                                                 | 1 | 1 | 1 | $= \mathbf{x} \cdot \mathbf{y} + \mathbf{x}' \cdot \mathbf{y}'$ | 1 | 1 | 1 |

| Inhibition                                                      | 0 | 0 | 0 | Complement of y                                                 | 0 | 0 | 1 |

| $\mathbf{F} = \mathbf{F}_2 = \mathbf{x} \cdot \mathbf{y'}$      | 0 | 1 | 0 | $\mathbf{F} = \mathbf{F}_{10} = \mathbf{y'}$                    | 0 | 1 | 0 |

| (x true, but y false)                                           | 1 | 0 | 1 |                                                                 | 1 | 0 | 1 |

|                                                                 | 1 | 1 | 0 |                                                                 | 1 | 1 | 0 |

| Transfer                                                        | 0 | 0 | 0 | Implication                                                     | 0 | 0 | 1 |

| $F = F_3 = x$                                                   | 0 | 1 | 0 | $F = F_{11} = x + y'$                                           | 0 | 1 | 0 |

| (Transfer x)                                                    | 1 | 0 | 1 | (If y = 1, F = x)                                               | 1 | 0 | 1 |

|                                                                 | 1 | 1 | 1 | If $y = 0$ , $F = y'$ )                                         | 1 | 1 | 1 |

| Inhibition                                                      | 0 | 0 | 0 | Complement of x                                                 | 0 | 0 | 1 |

| $\mathbf{F} = \mathbf{F}_4 = \mathbf{x'} \cdot \mathbf{y}$      | 0 | 1 | 1 | $F = F_{12} = x'$                                               | 0 | 1 | 1 |

| (y true, but x false)                                           | 1 | 0 | 0 |                                                                 | 1 | 0 | 0 |

|                                                                 | 1 | 1 | 0 |                                                                 | 1 | 1 | 0 |

| Transfer                                                        | 0 | 0 | 0 | Implication                                                     | 0 | 0 | 1 |

| $F = F_5 = y$                                                   | 0 | 1 | 1 | $F = F_{13} = x' + y$                                           | 0 | 1 | 1 |

| (Transfer y)                                                    | 1 | 0 | 0 | (If x = 1, F = y                                                | 1 | 0 | 0 |

|                                                                 | 1 | 1 | 1 | If $x = 0, F = x'$ )                                            | 1 | 1 | 1 |

| XOR operation                                                   | 0 | 0 | 0 | NAND operation                                                  | 0 | 0 | 1 |

| $F = F_6 = x \oplus y$                                          | 0 | 1 | 1 | $\mathbf{F} = \mathbf{F}_{14} = (\mathbf{x} \cdot \mathbf{y})'$ | 0 | 1 | 1 |

| $= \mathbf{x} \cdot \mathbf{y'} + \mathbf{x'} \cdot \mathbf{y}$ | 1 | 0 | 1 |                                                                 | 1 | 0 | 1 |

|                                                                 | 1 | 1 | 0 |                                                                 | 1 | 1 | 0 |

| OR operation                                                    | 0 | 0 | 0 | Identity                                                        | 0 | 0 | 1 |

| $\mathbf{F} = \mathbf{F}_7 = \mathbf{x} + \mathbf{y}$           | 0 | 1 | 1 | $F = F_{15} = 1$                                                | 0 | 1 | 1 |

|                                                                 | 1 | 0 | 1 |                                                                 | 1 | 0 | 1 |

|                                                                 | 1 | 1 | 1 |                                                                 | 1 | 1 | 1 |

# **Summary of Logic Gates**

The AND, OR and NOT are basic gates. Using these basic gates some more useful logical operations can be defined. They are NAND, NOR, Exclusive-OR (XOR) and Exclusive-NOR (XNOR).

Besides logic gates, buffers or drivers are also used in digital circuits to augment or increase current levels of signals where ever required.

The summary of popular logic gates used in digital electronics are listed in Table 1.16.

(AU, Nov/Dec'22, 13 Marks)

| Gate                           | Symbol            | Truth Table                                                                                                                                               |

|--------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| AND Gate                       | x x.y             | x         y         x . y           0         0         0           0         1         0           1         0         0           1         1         1 |

| OR Gate                        | x y x+y           | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                    |

| Inverter Gate<br>(or NOT gate) | x                 | x         x'           0         1           1         0                                                                                                  |

| Buffer                         | x x               | x<br>0<br>1                                                                                                                                               |

| NAND Gate                      | x <b>o</b> (x.y)' | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                    |

# Table 1.16: Continued...

| Gate                                          | Symbol                                                          | Truth Table                                                                                                                                                                                                                |

|-----------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOR Gate                                      | x $y$ $(x + y)'$                                                | x     y     x + y     (x + y)'       0     0     0     1       0     1     1     0       1     0     1     0       1     1     1     0                                                                                     |

| Exclusive-OR Gate (XOR)                       | $x \xrightarrow{x.y'+x'.y} = x \oplus y$                        | x     y     x · y'     x' · y     x $\oplus$ y       0     0     0     0     0       0     1     0     1     1       1     0     1     0     1       1     1     0     0     0                                             |

| Exclusive-NOR Gate (XNOR)<br>(or equivalence) | $x \xrightarrow{y} x.y + x'.y'$ $= (x \oplus y)'$ $= x \odot y$ | x         y         x $\oplus$ y $(x \oplus y)' = x \odot y$ 0         0         0         1           0         1         1         0           1         0         1         0           1         1         0         1 |

*Note: Bubble at output of gate indicates NOT operation.*

## Example 1.2

Prove the following identity.

- **a)** AB + A(B + C) + B(B + C) = B + AC

- **b)** AB + A'B + A'B' = A' + B

- c) AB'C + A'BC + ABC = AC + BC

#### Solution

a)

$$AB + A(B + C) + B(B + C) = AB + AB + AC + BB + BC$$

$= AB + AC + B + BC$

$BAB + AC + B + BC$

$= B(A + 1 + C) + AC = B.1 + AC$

$= B + AC$

b)  $AB + A'B + A'B' = AB + A'(B + B')$

$= AB + A'.1 = AB + A'$

$= (A' + A) (A' + B) = 1.(A' + B)$

$= A' + B$

c)  $AB'C + A'BC + ABC = ABC + AB'C + A'BC + ABC$

$= AC (B + B') + BC (A + A')$

$= AC + BC$

| x + x                                   | ( = x              |

|-----------------------------------------|--------------------|

| Repeated terms are considered once. x x | ( = x              |

| 1 + >                                   | ( = 1              |

|                                         |                    |

| x + x                                   | ('= 1              |

|                                         | ]                  |

|                                         |                    |

|                                         |                    |

|                                         |                    |

|                                         |                    |

| x + x                                   | ( <sup>'</sup> = 1 |

x + x' = 1

Using DeMorgan's theorem

$x \oplus y = xy' + x'y$

## Example 1.3

Prove the following identity using Boolean algebra:

$$(A + B)(A + (AB)')C + A'(B + C') + A'B + ABC = C(A + B) + A'(B + C')$$

#### Solution

L.H.S =

$$(A + B) (A + (AB)')C + A'(B + C') + A'B + ABC$$

R.H.S =  $C (A + B) + A'(B + C')$

L.H.S =  $(A + B) (A + (AB)')C + A'(B + C') + A'B + ABC$

=  $(A + B) (A + A' + B')C + A'(B + C') + A'(B + ABC)$

=  $(A + B) (A + A' + B')C + A'(B + A'C' + B(A' + AC))$

=  $(A + B) (1 + B')C + A'B + A'C' + B((A' + A)(A' + C)))$

=  $(A + B) 1.C + A'B + A'C' + B(1.(A' + C)))$

=  $AC + BC + A'B + A'C' + B(A' + C)$

=  $AC + BC + A'B + A'C' + B(A' + C)$

=  $AC + BC + A'B + A'C' + A'B + BC$

=  $AC + BC + A'B + A'C' + A'B + BC$

=  $AC + BC + A'C' + A'B$

=  $C (A + B) + A'(B + C')$

= RHS

#### Example 1.4

Prove the following:

a)  $A \oplus B = A' \oplus B'$ **b)**  $(A \oplus B)' = A \oplus B' = A' \oplus B$

#### Solution

**b)**  $(A \oplus B)' = A \oplus B' = A' \oplus B$  $A \oplus B' = A(B')' + A'B'$  $= AB + A'B' = (A \oplus B)'$  $A' \oplus B = A'B' + (A')'B$  $= A'B' + AB = (A \oplus B)'$

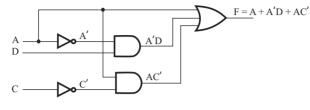

#### 1.4.1 Universal Gates

NAND and NOR gates are called *universal gates*, because any Boolean function can be realized only using NAND gates or only using NOR gates.

The NAND gate is a combination of AND followed by NOT gate. The NOR gate is a combination of OR followed by NOT gate.

# Table 1.17: Truth Table of NAND Gate

| x | у | (x . y)' |

|---|---|----------|

| 0 | 0 | 1        |

| 0 | 1 | 1        |

| 1 | 0 | 1        |

| 1 | 1 | 0        |

# Table 1.18: Truth Table of NOR Gate

| X | у | $(\mathbf{x} + \mathbf{y})'$ |

|---|---|------------------------------|

| 0 | 0 | 1                            |

| 0 | 1 | 0                            |

| 1 | 0 | 0                            |

| 1 | 1 | 0                            |

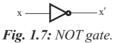

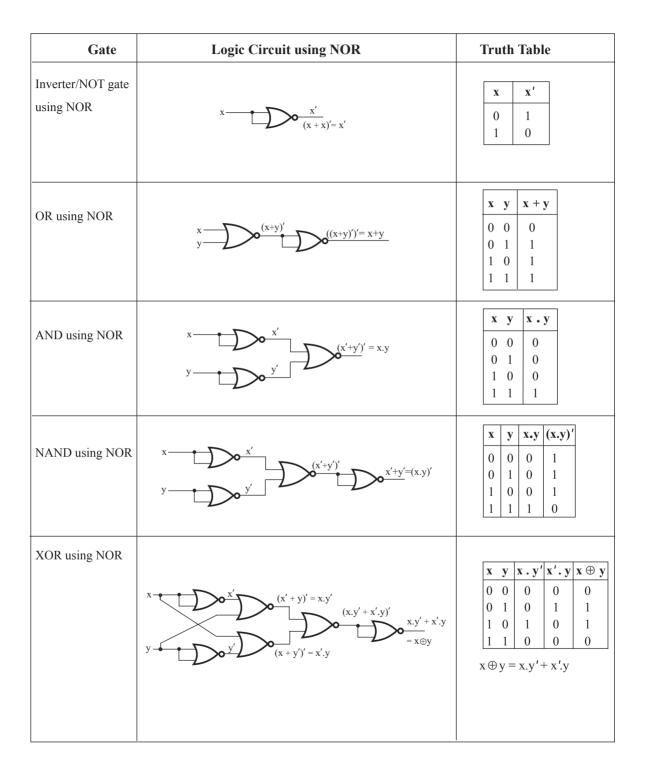

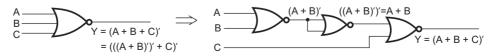

The realization of basic gates using only NAND gates are shown in Table 1.19.

The realization of basic gates using only NOR gates are shown in Table 1.20.

## Table 1.19: Realization of Basic Logic Gates using NAND Gates

| Gate                         | Logic Circuit using NAND                                                                                                                 | Truth Table                                                                                                                                                                                                       |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inverter/NOT gate using NAND | x                                                                                                                                        | x         x'           0         1           1         0                                                                                                                                                          |

| AND using NAND               | x y (x.y)' ((x.y)')' = x.y ((x.y)')' = x.y                                                                                               | x         y         x . y           0         0         0           0         1         0           1         1         1                                                                                         |

| OR using NAND                | x - b x' $y - b y'$ $y - b y'$                                                                                                           | $\mathbf{x}$ $\mathbf{y}$ $\mathbf{x}$ $\mathbf{y}$ 0         0         0         0           0         1         1         1           1         0         1         1           1         1         1         1 |

| NOR using NAND               |                                                                                                                                          | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                            |

| XOR using NAND               | $x \xrightarrow{x'} (x'.y)' \xrightarrow{(x'.y)'} ((x'.y)'.(x.y')')'$ $y \xrightarrow{y'} (x.y')' \xrightarrow{y'} (x.y')' = x \oplus y$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                            |

# Table 1.20: Realization of Basic Logic Gates using NOR Gates

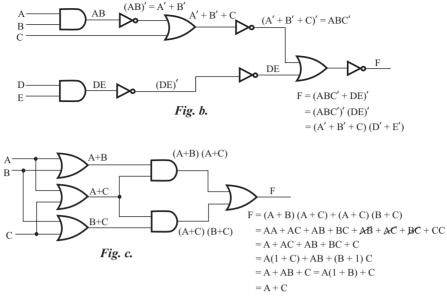

## 1.4.2 Positive and Negative Logic Gates

In positive logic, 1 is logic **high** and 0 is logic **low**. In negative logic, 0 is logic **high** and 1 is logic **low**. The logic gates discussed in Section 1.4 are positive logic gates which means that the logic levels of inputs and outputs are positive logic levels.

Logic gates can also be designed to work with negative logic levels. The AND and OR operation in positive and negative logic are given below:

In this book, only positive logic gates are used for analysis and design of digital logic circuit.

AND operation: AND operation of two or more variables is high only if all the variables are high.

|          | <u>e 1.21: Truth Table of Positive</u><br>Logic AND Gate |          |         | Table 1.22: Truth Table of NegaLogic AND Gate |          |  |  |

|----------|----------------------------------------------------------|----------|---------|-----------------------------------------------|----------|--|--|

| Ī        |                                                          |          |         |                                               |          |  |  |

| Inp      | Inputs Out                                               |          | I       | nputs                                         | Output   |  |  |

| a        | b                                                        | a.b      | a       | b                                             | a.b      |  |  |

| 0 (low)  | 0 (low)                                                  | 0 (low)  | 0 (high | ) 0 (high)                                    | 0 (high) |  |  |

| 0 (low)  | 1 (high)                                                 | 0 (low)  | 0 (high | ) 1 (low)                                     | 1 (low)  |  |  |

| 1 (high) | 0 (low)                                                  | 0 (low)  | 1 (low) | 0 (high)                                      | 1 (low)  |  |  |

| 1 (high) | 1 (high)                                                 | 1 (high) | 1 (low) | 1 (low)                                       | 1 (low)  |  |  |

OR operation: OR operation of two or more variables is high if one of the variable is high.

Table 1.23: Truth Table of Positive Logic OR Gate

| Inp      | Output   |          |

|----------|----------|----------|

| a b      |          | a + b    |

| 0 (low)  | 0 (low)  | 0 (low)  |

| 0 (low)  | 1 (high) | 1 (high) |

| 1 (high) | 0 (low)  | 1 (high) |

| 1 (high) | 1 (high) | 1 (high) |

Table 1.24: Truth Table of Negative Logic OR Gate

| Inp      | Output   |          |

|----------|----------|----------|

| a b      |          | a + b    |

| 0 (high) | 0 (high) | 0 (high) |

| 0 (high) | 1 (low)  | 0 (high) |

| 1 (low)  | 0 (high) | 0 (high) |

| 1 (low)  | 1 (low)  | 1 (low)  |

In order to differentiate negative logic level gates from the positive logic level gates, a bubble is added at every input and output. The bubble basically represent an inverter which is used to invert the logic levels. When a bubble is added to the output end that already has a bubble then it represents double time inversion and so that output end will not have a bubble in negative logic representation. The conversion of positive logic level gates to negative logic level gates are listed in Table 1.25.

| Gate          | Positive Logic                                | Negative Logic                        |

|---------------|-----------------------------------------------|---------------------------------------|

| AND Gate      | x $y$ $z = x.y$                               | xo                                    |

| OR Gate       | x $y$ $z = x+y$                               | $x - y' - \frac{z - (x' + y')'}{2}$   |

| Inverter Gate | x                                             | x x'                                  |

| Buffer        | x                                             | x                                     |

| NAND Gate     | x - y - y - y - y - y - y - y - y - y -       | x z = x'.y'                           |

| NOR Gate      | $x = \sum_{y = -\infty} \frac{z - (x+y)'}{2}$ | $x \underbrace{z = x' + y'}_{y}$      |

| XOR gate      | $x$ $y$ $z = x \oplus y$                      | $x \underbrace{z = x' \oplus y'}_{y}$ |

Table 1.25: Summary of Positive and Negative Logic Gates

Using the output equations of logic gates listed in Table 1.25, the truth table of positive and negative logic gates are obtained as shown in Tables 1.26 to 1.29.

## Table 1.26: Truth Table of AND Gate

| a) Positive Logic |     |                 |  |

|-------------------|-----|-----------------|--|

| Inp               | uts | Output          |  |

| X                 | у   | $z = x \cdot y$ |  |

| 0                 | 0   | 0               |  |

| 0                 | 1   | 0               |  |

| 1                 | 0   | 0               |  |

| 1                 | 1   | 1               |  |

| b) | Negative | Logic |

|----|----------|-------|

|    |          |       |

| Inp | outs | Complement<br>of Inputs |    | Output                                          |

|-----|------|-------------------------|----|-------------------------------------------------|

| x   | у    | x'                      | у′ | $\mathbf{z} = (\mathbf{x'} \cdot \mathbf{y'})'$ |

| 0   | 0    | 1                       | 1  | 0                                               |

| 0   | 1    | 1                       | 0  | 1                                               |

| 1   | 0    | 0                       | 1  | 1                                               |

| 1   | 1    | 0                       | 0  | 1                                               |

# Table 1.27: Truth Table of OR Gate

| Inp | uts | Output                                 |

|-----|-----|----------------------------------------|

| X   | У   | $\mathbf{z} = \mathbf{x} + \mathbf{y}$ |

| 0   | 0   | 0                                      |

| 0   | 1   | 1                                      |

| 1   | 0   | 1                                      |

| 1   | 1   | 1                                      |

| ł | b) Negative Logic |   |                         |    |                |  |

|---|-------------------|---|-------------------------|----|----------------|--|

|   | Inputs            |   | Complement<br>of Inputs |    | Output         |  |

|   | X                 | у | x'                      | у′ | z = (x' + y')' |  |

|   | 0                 | 0 | 1                       | 1  | 0              |  |

|   | 0                 | 1 | 1                       | 0  | 0              |  |

|   | 1                 | 0 | 0                       | 1  | 0              |  |

|   | 1                 | 1 | 0                       | 0  | 1              |  |

In negative logic AND gate,

$z = (x', y')' \implies z = x + y$

Therefore, we can say that the negative logic AND gate is same as positive logic OR gate.

In negative logic OR gate,

$z = (x' + y')' \implies z = x \cdot y$

Therefore, we can say that the negative logic OR gate is same as positive logic AND gate.

## Table 1.28: Truth Table of NAND Gate

a) Positive Logic

| Inputs |   | Output                                        |

|--------|---|-----------------------------------------------|

| x y    |   | $\mathbf{z} = (\mathbf{x} \cdot \mathbf{y})'$ |

| 0      | 0 | 1                                             |

| 0      | 1 | 1                                             |

| 1      | 0 | 1                                             |

| 1      | 1 | 0                                             |

| Inputs |   | Complement<br>of Inputs |    | Output            |

|--------|---|-------------------------|----|-------------------|

| x      | у | x'                      | y' | $z = x' \cdot y'$ |

| 0      | 0 | 1                       | 1  | 1                 |

| 0      | 1 | 1                       | 0  | 0                 |

| 1      | 0 | 0                       | 1  | 0                 |

| 1      | 1 | 0                       | 0  | 0                 |

## Table 1.29: Truth Table of NOR Gate

a) Positive Logic

b) Negative Logic

| Inputs |   | Output                                    |  |  |

|--------|---|-------------------------------------------|--|--|

| x y    |   | $\mathbf{z} = (\mathbf{x} + \mathbf{y})'$ |  |  |

| 0      | 0 | 1                                         |  |  |

| 0      | 1 | 0                                         |  |  |

| 1      | 0 | 0                                         |  |  |

| 1      | 1 | 0                                         |  |  |

| Inputs |   | Compl<br>of In |    | Output                                   |

|--------|---|----------------|----|------------------------------------------|

| X      | у | x'             | y' | $\mathbf{z} = \mathbf{x}' + \mathbf{y}'$ |

| 0      | 0 | 1              | 1  | 1                                        |

| 0      | 1 | 1              | 0  | 1                                        |

| 1      | 0 | 0              | 1  | 1                                        |

| 1      | 1 | 0              | 0  | 0                                        |

In negative logic NAND gate,

$z = x' \cdot y' \implies z = (x + y)'$

Therefore, we can say that the negative logic NAND gate is same as positive logic NOR gate.

In negative logic NOR gate,

$z = x' + y' \implies z = (x \cdot y)'$

Therefore, we can say that the negative logic NOR gate is same as positive logic NAND gate.

# **1.5 Boolean Functions**

A *Boolean function* is described by a Boolean expression which consists of binary variables, binary constants 0 and 1 and logical operators, AND, OR and NOT. Binary variables are denoted by either lower case (a, b, c, ...., x, y, z) or upper case (A, B, C, ....., X, Y, Z) alphabets.

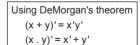

Using DeMorgan's theorem

Using DeMorgan's theorem

Using DeMorgan's theorem

Using DeMorgan's theorem

Some examples of Boolean functions are given below:

$$F = (x . y) + z'$$

$$F_{1} = (x . z) + y'$$

$$F_{2} = (x . y . z) + (y . z')$$

Alternatively,

$F(x, y, z) = (x \cdot y) + z'$

$$F_{1}(x, y, z) = (x \cdot z) + y'$$

F\_{2}(x, y, z) = (x \cdot y \cdot z) + (y \cdot z')

A Boolean function can be evaluated for all possible combinations of binary values of the variables of the function. The variables of a function are also known as *input variables* or *inputs*.

Let, n = Number of variables in a Boolean function

$2^n$  = Number of combinations of binary values of n variables.

Truth table for a Boolean function can be constructed with 2<sup>n</sup> combinations of n input variables.

*Note:* To simplify Boolean expression dot or AND operation is represented without operator.  $x \cdot y \Rightarrow xy$   $y \cdot z \Rightarrow yz$   $x \cdot y \cdot z \Rightarrow xyz$

## Example 1.5

Construct the truth table for the following functions.

**a)**

$$F_1 = xy + xy' + y'z$$

**b)**  $F_2 = bc + a'c'$

## Solution

```

a) F_1 = xy + xy' + y'z

```

```

Table 1: Truth Table of Function, F<sub>1</sub>

```

| Input Variables<br>and Complement |   |   |    | Product<br>Terms |      |     | Function<br>Output |

|-----------------------------------|---|---|----|------------------|------|-----|--------------------|

| x                                 | У | z | У' | ху               | x y' | y'z | F <sub>1</sub>     |

| 0                                 | 0 | 0 | 1  | 0                | 0    | 0   | 0                  |

| 0                                 | 0 | 1 | 1  | 0                | 0    | 1   | 1                  |

| 0                                 | 1 | 0 | 0  | 0                | 0    | 0   | 0                  |

| 0                                 | 1 | 1 | 0  | 0                | 0    | 0   | 0                  |

| 1                                 | 0 | 0 | 1  | 0                | 1    | 0   | 1                  |

| 1                                 | 0 | 1 | 1  | 0                | 1    | 1   | 1                  |

| 1                                 | 1 | 0 | 0  | 1                | 0    | 0   | 1                  |

| 1                                 | 1 | 1 | 0  | 1                | 0    | 0   | 1                  |

**b)**  $F_{2} = bc + a'c'$

Table 1: Truth Table of Function, F,

| i |   | t Varia<br>omple | ables<br>ements | Product<br>Terms |    | Function<br>Output |                       |

|---|---|------------------|-----------------|------------------|----|--------------------|-----------------------|

| а | b | С                | a'              | C'               | bc | a'c'               | <b>F</b> <sub>2</sub> |

| 0 | 0 | 0                | 1               | 1                | 0  | 1                  | 1                     |

| 0 | 0 | 1                | 1               | 0                | 0  | 0                  | 0                     |

| 0 | 1 | 0                | 1               | 1                | 0  | 1                  | 1                     |

| 0 | 1 | 1                | 1               | 0                | 1  | 0                  | 1                     |

| 1 | 0 | 0                | 0               | 1                | 0  | 0                  | 0                     |

| 1 | 0 | 1                | 0               | 0                | 0  | 0                  | 0                     |

| 1 | 1 | 0                | 0               | 1                | 0  | 0                  | 0                     |

| 1 | 1 | 1                | 0               | 0                | 1  | 0                  | 1                     |

#### Example 1.6

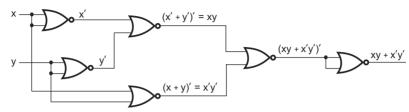

Realize 2-input XNOR gate using NOR gates.

#### Solution

The XNOR operation is given by the following Boolean equation.

$x \odot y = xy + x'y'$

The above equation can be implemented using NOR gate as shown in Fig. 1.

Fig. 1: XNOR operation using only NOR gates.

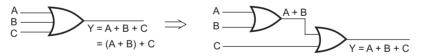

## Example 1.7

Realize the 3-input gate using 2-input gates for the folowing gates:

a) AND b) OR c) NAND d) NOR

#### Solution

a) AND

Fig. 1: 3-input AND gate using 2-input AND gate.

b) OR

Fig. 2: 3-input OR gate using 2-input OR gate.

c) NAND

Fig. 3: 3-input NAND gate using 2-input NAND gate.

d) NOR

Fig. 4: 3-input NOR gate using 2-input NOR gate.

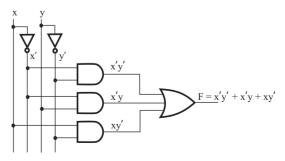

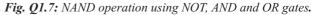

# 1.5.1 Implementation of Boolean Functions by Logic Gates

A Boolean function basically involves product of variables, sum of variables and complement of variables. Therefore, the straight forward implementation of Boolean function can be made by using basic gates AND, OR and NOT. The complement of a variable is obtained using NOT gate. The product term is realized using AND gate. The sum term is realized using OR gate.

## Example 1.8

Implement the following functions using basic logic gates.

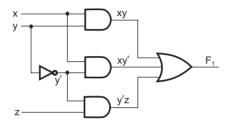

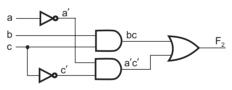

**a)**  $F_1 = xy + xy' + y'z$  **b)**  $F_2 = bc + a'c'$

## Solution

a)  $F_1 = xy + xy' + y'z$

Fig. 1: Logic circuit for function, F<sub>1</sub>.

b)

$$F_2 = bc + a'c'$$

**Fig. 2:** Logic circuit for function,  $F_2$ .

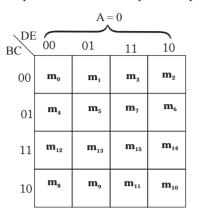

## 1.5.2 Minterms

*Minterms* are 2<sup>n</sup> possible combinations of AND terms (or product terms) with n variables such that the logical AND of all the variables is 1.

The minterms can be formed with two, three, four, ..... variables. The  $2^n$  minterms are denoted as  $m_0, m_1, m_2, m_3, \dots, m_q$  where  $q = 2^n - 1$ .

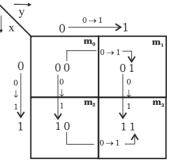

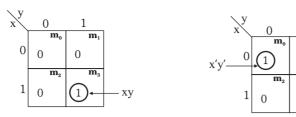

The  $2^n$  combination of AND terms, for n = 2 and 3 are shown below. The AND terms are formed from  $2^n$  combinations of n-bit binary. In AND terms a literal is primed if its value is 0 and unprimed if its value is 1. So that the AND of all literals is always 1.

Let, n = 2

Let x and y be the two variables to denote the two bits of binary.

When n = 2,  $2^n = 2^2 = 4$

Therefore, four combinations of AND terms with two variables are possible as shown below:

| 0 0              | x'. y' (0'. 0'=1)             | $x'y' = m_0$                       |

|------------------|-------------------------------|------------------------------------|

| $01 \Rightarrow$ | x'. y (0'. 1 = 1)             | $\Rightarrow$ x'y = m <sub>1</sub> |

| 10               | $x \cdot y' (1 \cdot 0' = 1)$ | $x y' = m_2$                       |

| 11               | $x \cdot y  (1 \cdot 1 = 1)$  | $x y = m_3$                        |

## Let, n = 3

Let x, y and z be the three variables to denote the three bits of binary.

When n = 3,  $2^n = 2^3 = 8$

Therefore, eight combinations of AND terms with three variables are possible as shown below:

| 0 ( | 0 0 |               | $x^{\prime}.y^{\prime}.z^{\prime}$ | (0'. 0'. 0'=1) |               | $x'y'z' = m_0$ |

|-----|-----|---------------|------------------------------------|----------------|---------------|----------------|

| 0 ( | 01  | $\Rightarrow$ | x'.y'.z                            | (0'.0'.1=1)    | $\Rightarrow$ | $x'y' z = m_1$ |

| 0   | 10  |               | $x^{\prime}.y^{}.z^{\prime}$       | (0'.1.0'=1)    |               | $x'y z' = m_2$ |

| 0   | 11  |               | x'.y.z                             | (0'.1.1=1)     |               | $x'yz = m_3$   |

| 1 ( | 0 0 |               | x . y' . z'                        | (1.0'.0'=1)    |               | x y'z' = $m_4$ |

| 1 ( | 01  | $\Rightarrow$ | x.y'.z                             | (1.0'.1=1)     | $\Rightarrow$ | $x y'z = m_5$  |

| 1   | 10  |               | x.y.z'                             | (1.1.0'=1)     |               | x y $z' = m_6$ |

| 1   | 11  |               | x.y.z                              | (1.1.1=1)      |               | $x y z = m_7$  |

## Table 1.30: Two-Variable Minterms

| x | у | Minterm | Notation       |

|---|---|---------|----------------|

| 0 | 0 | x'. y'  | m <sub>0</sub> |

| 0 | 1 | х'. у   | m <sub>1</sub> |

| 1 | 0 | х.у′    | m <sub>2</sub> |

| 1 | 1 | х.у     | m <sub>3</sub> |

#### **Table 1.31: Three-Variable Minterms**

| x | у | z | Minterm    | Notation       |

|---|---|---|------------|----------------|

| 0 | 0 | 0 | x'. y'. z' | m <sub>0</sub> |

| 0 | 0 | 1 | x'. y'. z  | m <sub>1</sub> |

| 0 | 1 | 0 | x'. y. z'  | m <sub>2</sub> |

| 0 | 1 | 1 | x'. y. z   | m <sub>3</sub> |

| 1 | 0 | 0 | x . y'. z' | m <sub>4</sub> |

| 1 | 0 | 1 | x . y'. z  | m <sub>5</sub> |

| 1 | 1 | 0 | x.y.z'     | m <sub>6</sub> |

| 1 | 1 | 1 | x . y . z  | m <sub>7</sub> |

Table 1.32: Four-Variable Minterms

| a | b | c | d | Minterm        | Notation        |

|---|---|---|---|----------------|-----------------|

| 0 | 0 | 0 | 0 | a'.b'.c'.d'    | m <sub>0</sub>  |

| 0 | 0 | 0 | 1 | a'.b'.c'.d     | m <sub>1</sub>  |

| 0 | 0 | 1 | 0 | a'.b'.c.d'     | m <sub>2</sub>  |

| 0 | 0 | 1 | 1 | a'.b'.c.d      | m <sub>3</sub>  |

| 0 | 1 | 0 | 0 | a'.b.c'.d'     | m <sub>4</sub>  |

| 0 | 1 | 0 | 1 | a'.b.c'.d      | m <sub>5</sub>  |

| 0 | 1 | 1 | 0 | a'.b.c.d'      | m <sub>6</sub>  |

| 0 | 1 | 1 | 1 | a'.b.c.d       | m <sub>7</sub>  |

| 1 | 0 | 0 | 0 | a . b'. c'. d' | m <sub>8</sub>  |

| 1 | 0 | 0 | 1 | a .b'.c'.d     | m <sub>9</sub>  |

| 1 | 0 | 1 | 0 | a . b'. c . d' | m <sub>10</sub> |

| 1 | 0 | 1 | 1 | a .b'.c.d      | m <sub>11</sub> |

| 1 | 1 | 0 | 0 | a . b . c'. d' | m <sub>12</sub> |

| 1 | 1 | 0 | 1 | a .b .c'.d     | m <sub>13</sub> |

| 1 | 1 | 1 | 0 | a .b .c. d'    | m <sub>14</sub> |

| 1 | 1 | 1 | 1 | a .b .c. d     | m <sub>15</sub> |

#### 1.5.3 Maxterms

*Maxterms* are  $2^n$  possible combinations of OR terms (or sum terms) with n variables such that the logical OR of all the variables is 0.

The maxterms can be formed with two, three, four, ...... variables.

The  $2^n$  maxterms are denoted as  $M_0$ ,  $M_1$ ,  $M_2$ ,  $M_3$ , ....,  $M_q$  where  $q = 2^n - 1$ .

The  $2^n$  combinations of OR terms, for n = 2 and 3 are shown below. The OR terms are formed from  $2^n$  combinations of n-bit binary. In OR terms a literal is primed if its value is 1, and unprimed if its value is 0 so that the OR of all literals is always 0.

Let, n = 2

Let x and y be the two variables to denote two bits of binary.

When n = 2,  $2^n = 2^2 = 4$

Therefore, four combinations of OR terms with two variables are possible as shown below:

| 0 0                 | $\mathbf{x} + \mathbf{y}$ | (0+0 = 0)             | $\mathbf{x} + \mathbf{y} = \mathbf{M}_0$  |

|---------------------|---------------------------|-----------------------|-------------------------------------------|

| 0 1                 | $x + y^{\prime}$          | (0 + 1' = 0)          | $x + y' = M_1$                            |

| $1 \ 0 \Rightarrow$ | x' + y                    | $(1'+0 = 0) \implies$ | $\mathbf{x'} + \mathbf{y} = \mathbf{M}_2$ |

| 1 1                 | $x^{\prime} + y^{\prime}$ | (1'+1'=0)             | $x' + y' = M_3$                           |

Let, n = 3

Let x, y and z be the three variables to denote three bits of binary.

When n = 3,  $2^n = 2^3 = 8$

Therefore, eight combinations of OR terms with three variables are possible as shown below:

| 0 0 0                     | x + y + z   | (0 + 0 + 0 = 0)                 | $x + y + z = M_0$                                       |

|---------------------------|-------------|---------------------------------|---------------------------------------------------------|

| 0 0 1                     | x + y + z'  | (0 + 0 + 1' = 0)                | $\mathbf{x} + \mathbf{y} + \mathbf{z'} = \mathbf{M}_1$  |

| 0 1 0                     | x + y' + z  | (0 + 1' + 0 = 0)                | $x + y' + z = M_2$                                      |

| $0 \ 1 \ 1 \ \Rightarrow$ | x + y' + z' | $(0 + 1' + 1' = 0) \Rightarrow$ | $x + y' + z' = M_3$                                     |

| 1 0 0                     | x' + y + z  | (1'+ 0 + 0 = 0)                 | $x' + y + z = M_4$                                      |

| 1 0 1                     | x' + y + z' | (1'+ 0 + 1'=0)                  | $x' + y + z' = M_5$                                     |

| 1 1 0                     | x'+y'+z     | (1' + 1' + 0 = 0)               | $\mathbf{x'} + \mathbf{y'} + \mathbf{z} = \mathbf{M}_6$ |

| 1 1 1                     | x'+y'+z'    | (1'+1'+1'=0)                    | $x' + y' + z' = M_7$                                    |

## Table 1.33: Two-Variable Maxterms

| x | у | Maxterm | Notation       |

|---|---|---------|----------------|

| 0 | 0 | x + y   | M <sub>0</sub> |

| 0 | 1 | x + y'  | M <sub>1</sub> |

| 1 | 0 | х'+ у   | M <sub>2</sub> |

| 1 | 1 | x'+y'   | M <sub>3</sub> |

## **Table 1.34: Three-Variable Maxterms**

| x | у | z | Maxterm     | Notation       |

|---|---|---|-------------|----------------|

| 0 | 0 | 0 | x + y + z   | M <sub>0</sub> |

| 0 | 0 | 1 | x + y + z'  | $M_1$          |

| 0 | 1 | 0 | x + y' + z  | M <sub>2</sub> |

| 0 | 1 | 1 | x + y' + z' | M <sub>3</sub> |

| 1 | 0 | 0 | x' + y + z  | M <sub>4</sub> |

| 1 | 0 | 1 | x' + y + z' | M <sub>5</sub> |

| 1 | 1 | 0 | x' + y' + z | M <sub>6</sub> |

| 1 | 1 | 1 | x'+y'+z'    | M <sub>7</sub> |

| a | b | c | d | Maxterm          | Notation        |  |  |

|---|---|---|---|------------------|-----------------|--|--|

| 0 | 0 | 0 | 0 | a + b + c + d    | M <sub>0</sub>  |  |  |

| 0 | 0 | 0 | 1 | a+b+c+d'         | M <sub>1</sub>  |  |  |

| 0 | 0 | 1 | 0 | a+b+c'+d         | M <sub>2</sub>  |  |  |

| 0 | 0 | 1 | 1 | a + b + c' + d'  | M <sub>3</sub>  |  |  |

| 0 | 1 | 0 | 0 | a+b'+c+d         | M <sub>4</sub>  |  |  |

| 0 | 1 | 0 | 1 | a + b' + c + d'  | M <sub>5</sub>  |  |  |

| 0 | 1 | 1 | 0 | a+b'+c'+d        | M <sub>6</sub>  |  |  |

| 0 | 1 | 1 | 1 | a + b' + c' + d' | M <sub>7</sub>  |  |  |

| 1 | 0 | 0 | 0 | a'+b+c+d         | M <sub>8</sub>  |  |  |

| 1 | 0 | 0 | 1 | a'+b + c + d'    | M <sub>9</sub>  |  |  |

| 1 | 0 | 1 | 0 | a'+b+c'+d        | M <sub>10</sub> |  |  |

| 1 | 0 | 1 | 1 | a'+b + c'+d'     | M <sub>11</sub> |  |  |

| 1 | 1 | 0 | 0 | a'+b'+c+d        | M <sub>12</sub> |  |  |

| 1 | 1 | 0 | 1 | a'+b'+c+d'       | M <sub>13</sub> |  |  |

| 1 | 1 | 1 | 0 | a'+b'+c'+d       | M <sub>14</sub> |  |  |

| 1 | 1 | 1 | 1 | a'+b'+c'+d'      | M <sub>15</sub> |  |  |

## Table 1.35: Four-Variable Maxterms

## 1.5.4 Standard Forms

There are three types of standard forms of expressing a Boolean function. They are,

- 1. Sum-of-products (SOP) form

- 2. Product-of-sums (POS) form

- 3. Canonical form

The *canonical form* is also expressed in SOP or POS form. The SOP or POS form is said to be canonical only if all the variables are present in every term of the SOP or POS form.

In SOP or POS form each term of the Boolean expression need not have all the variables of the function. Hence SOP and POS forms are also simplified forms of Boolean functions.

# 1.5.5 Sum-of-Products and Product-of-Sums Simplification

*Sum-of-products (SOP)* can be realized by AND operation of literals followed by OR operation of output of AND. Here, AND operation of literals are the products and OR operation of output of AND is the sum of product terms. *Product-of-sums (POS)* can be realized by OR operation of literals followed by AND operation of output of OR. Here, OR operation of literals are the sums and AND operation of output of OR is the product of sum terms. The realizations in SOP and POS forms are called *two-level realization of standard forms*.

The two-level realization of SOP form can be obtained by using AND gates to implement product terms followed by OR gate to get sum of product terms. The two-level realization of POS form can be obtained by using OR gates to implement sum terms followed by AND gate to get product of sum terms.

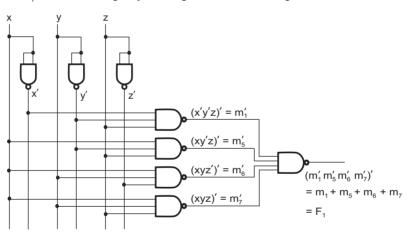

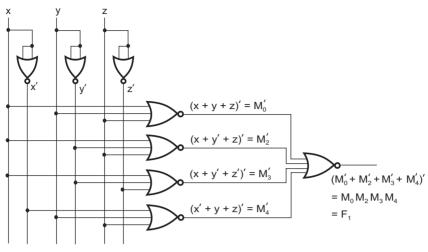

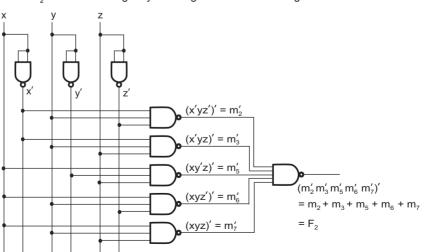

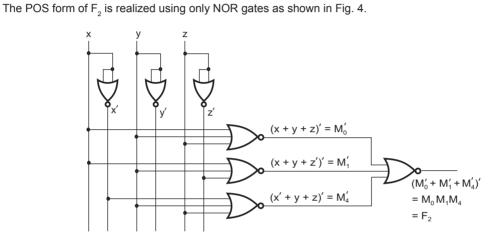

Since NAND and NOR gates are universal gates, the two-level realization of SOP form of a Boolean function can be obtained using only NAND gates. Similarly, two-level realization of POS form of a Boolean function can be obtained using only NOR gates.

## Example 1.9

Draw the two-level realization of the following functions.

**a)**

$$F_1 = y' + xy + x'yz'$$

**b)**  $F_2 = x(y' + z)(x' + y + z')$

#### Solution

a)  $F_1 = y' + xy + x'yz'$  - Sum-of-products y' x y' x' y' y'y

## Example 1.10

Determine the complement of the following functions and show that SOP becomes POS and vice-versa.

**a)**  $F_1 = y' + xy + x'yz$  **b)**  $F_2 = x(y' + z)(x' + y + z')$

## Solution

a)  $F_1 = y' + xy + x'yz$  - Sum-of-products

$\bigcup_{i=1}^{i} \text{Complement}$   $F_{1}' = (y' + xy + x'yz)'$  = (y')'(xy)'(x'yz)' = y (x' + y') (x + y' + z') - Product-of-sums

b)  $F_2 = x (y' + z) (x' + y + z')$  - Product-of-sums

$\bigcup_{x = 1}^{1} Complement} F_{2}' = (x (y' + z) (x' + y + z'))'$ = x' + (y' + z)' + (x' + y + z')'= x' + (y z') + (x y' z) - Sum-of-products

#### Using DeMorgan's theorem (x + y)' = x'y' (x . y)' = x' + y'

Using DeMorgan's theorem (x + y)' = x'y' (x . y)' = x' + y'

## **1.5.6 Canonical Form**

A Boolean function can be expressed algebraically from its truth table by forming a minterm for each combination of the variables that produces a 1 in the output and then taking the OR of all the minterms.

Similarly, a Boolean function can be expressed algebraically from its truth table by forming a maxterm for each combination of the variable that produces a 0 in the output and then taking the AND of all the maxterm. A Boolean function expressed as a sum of minterms or product of maxterms are said to be in canonical form.

The given function can be expressed in canonical form without using truth table. For sum of minterms insert sum of missing literal and its complement with "." operation and expand. Similarly for product of maxterms insert product of missing literal and its complement with "+" operation and expand.

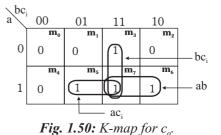

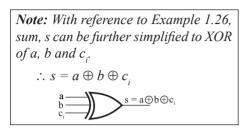

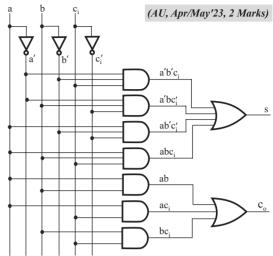

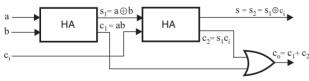

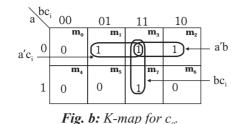

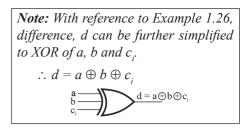

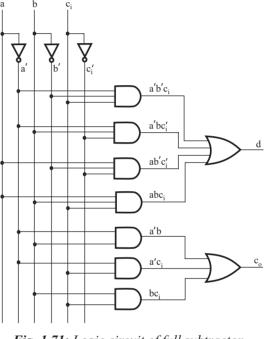

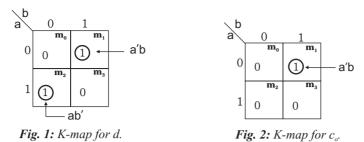

#### 1.26

## **1.5.7 Complement of a Function**

If, F is a function then F' is complement of F. The complement of a function can be directly evaluated using Boolean theorems and postulates. Alternatively, the complement can also be obtained by using duality. In duality replace "+" by "." and "." by "+" and variables by its complement.

It can be observed that complement of sum-of-products will be product-of-sums and vice-versa

i.e, Product-of-sums  $\stackrel{\text{Complement}}{\longleftarrow}$  Sum-of-products

Note: This concept holds good for complement of canonical forms also.

## Example 1.11

Determine the complement of the following Boolean functions.

**a)**

$$F_1 = xy + x'z$$

**b)**  $F_2 = wx + yz$  **c)**  $F_3 = xy' + x'y$

#### Solution

a)  $F_1 = xy + x'z$

#### Case i: Direct Evaluation of Complement

$F_{1} = x y + x' z$   $\bigcup \text{ Complement}$   $F_{1}' = (x y + x' z)'$   $= (x y)' \cdot (x' z)'$   $= (x' + y') \cdot ((x')' + z')$   $= (x' + y') \cdot (x + z')$

Case ii: Complement using Duality

$\begin{array}{rcl} x & . & y & + & x' . & z \\ \downarrow & \downarrow \downarrow & \downarrow & \downarrow & \downarrow & Replace by dual elements \\ (x' + y') . & (x + z') \\ & & \downarrow \\ (x' + y') . & (x + z') & = F_1' \end{array}$

b)  $F_2 = wx + yz$

#### **Case i: Direct Evaluation of Complement**

$F_{2} = w x + y z$   $\bigcup \text{ Complement}$   $F'_{2} = (w x + y z)'$   $= (w x)' \cdot (y z)'$   $= (w' + x') \cdot (y' + z')$

#### Case ii: Complement using Duality

$w \cdot x + y \cdot z$   $\downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow$   $(w' + x') \cdot (y' + z')$   $\bigcup \text{ Replace by dual elements}$   $(w' + x') \cdot (y' + z') = F'_2$

Using DeMorgan's theorem (x + y)' = x'y' $(x \cdot y)' = x' + y'$

c)  $F_3 = xy' + x'y$

**Case i: Direct Evaluation of Complement**

$F_{3} = x y' + x' y$   $\bigcup \text{ Complement}$   $F_{3}' = (x y' + x' y)'$   $= (x y')' \cdot (x' y)'$   $= (x' + y) \cdot (x + y')$

Case ii: Complement using Duality

$\begin{array}{cccc} x \ . \ y' \ + \ x'. \ y \\ \downarrow \ \downarrow \ \downarrow \ \downarrow \ \downarrow \ \downarrow \ Replace by dual elements \\ (x' + y) \ . \ (x + y') \\ & \downarrow \\ (x' + y) \ . \ (x + y') = F_3' \end{array}$

Using DeMorgan's theorem (x + y)' = x'y' (x . y)' = x' + y'

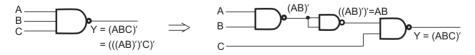

# **1.5.8 Implementation of Boolean Functions using Universal Gates**

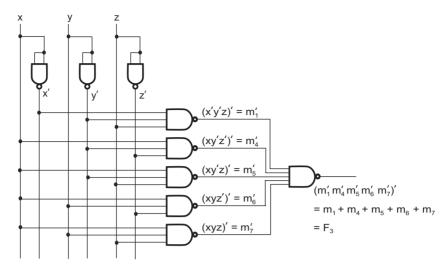

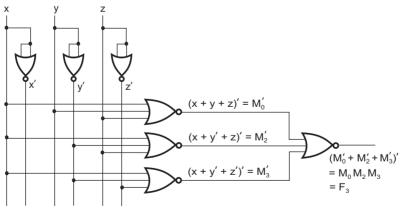

The NAND and NOR gates are called *universal gates*. When a Boolean function is expressed in SOP form, it can be realized using only NAND gates. When a Boolean function is expressed in POS form, it can be realized using only NOR gates.

#### Example 1.12

Express the function F = x + y'z, in sum of minterms and product of maxterms and verify the result by simplification using Boolean theorems and postulates.

#### Solution

| Input<br>Variables |   |   | Minterm        |        | Maxterm        |             | Complement<br>of y | Product<br>Term | Function<br>Output |

|--------------------|---|---|----------------|--------|----------------|-------------|--------------------|-----------------|--------------------|

| x                  | у | z |                |        |                |             | У'                 | y'z             | F                  |

| 0                  | 0 | 0 | m <sub>o</sub> | x'y'z' | M <sub>o</sub> | x + y + z   | 1                  | 0               | 0                  |

| 0                  | 0 | 1 | m,             | x'y'z  | M <sub>1</sub> | x + y + z'  | 1                  | 1               | 1                  |

| 0                  | 1 | 0 | m <sub>2</sub> | x'yz'  | M <sub>2</sub> | x + y' + z  | 0                  | 0               | 0                  |

| 0                  | 1 | 1 | m <sub>3</sub> | x'y z  | M <sub>3</sub> | x + y' + z' | 0                  | 0               | 0                  |

| 1                  | 0 | 0 | m <sub>4</sub> | x y'z' | M <sub>4</sub> | x'+y+z      | 1                  | 0               | 1                  |

| 1                  | 0 | 1 | m <sub>5</sub> | x y'z  | $M_5$          | x'+y+z'     | 1                  | 1               | 1                  |

| 1                  | 1 | 0 | m <sub>6</sub> | x y z' | M <sub>6</sub> | x'+y'+z     | 0                  | 0               | 1                  |

| 1                  | 1 | 1 | m <sub>7</sub> | x y z  | M <sub>7</sub> | x'+y'+z'    | 0                  | 0               | 1                  |

Table 1: Truth Table

A function can be expressed as a sum of minterms for which the function output is 1. Here, F is 1, when  $m_1$ ,  $m_4$ ,  $m_5$ ,  $m_6$  and  $m_7$  are inputs.

$$\therefore F = m_1 + m_4 + m_5 + m_6 + m_7$$

=  $\sum m(1, 4, 5, 6, 7) = x'y'z + xy'z' + xy'z + xyz' + xyz$

A function can be expressed as a product of maxterms for which the function output is 0. Here, F is 0, when  $M_0$ ,  $M_2$  and  $M_3$  are inputs

| F | $= M_{0} M_{2} M_{3}$                    |

|---|------------------------------------------|

|   | = ∏ M(0, 2, 3)                           |

|   | = (x + y + z) (x + y' + z) (x + y' + z') |

# Proof:

Case i:

$$F = m_{1} + m_{4} + m_{5} + m_{6} + m_{7}$$

$$= x'y'z + xy'z' + xy'z + xyz' + xyz$$

$$= x'y'z + xy'(z' + z) + xy(z' + z)$$

$$= x'y'z + xy' \cdot 1 + xy \cdot 1$$

$$= x'y'z' + xy' + xy$$

$$= x'y'z + x(y' + y)$$

$$= x'y'z + x \cdot 1$$

$$= x'y'z + x$$

$$= (x' + x)(y'z + x)$$

$$= 1 \cdot y'z + x$$

$$= x + y'z$$

Case ii:

$$F = M_0 M_2 M_3$$

= (x + y + z) (x + y' + z) (x + y' + z')

= (x + z + y) (x + z + y') (x + y' + z')

= (x + z + (y y')) (x + y' + z')

= (x + z + 0) (x + y' + z')

= x + (z (y' + z'))

= x + zy' + zz'

= x + y' z + 0

= x + y' z

| × | . x' = 0  |

|---|-----------|

| × | x + 0 = x |

#### Example 1.13

Express the Boolean function F(p, q, r) = (pq + r) (q + pr) as sum of minterms and product of maxterms.

#### Solution:

i) Sum of Minterms

F(p, q, r) = (pq + r)(q + pr)= pqq + pqpr + rq + rpr = pq + pqr + rq + rp = pq(r + r') + pqr + rq(p + p') + rp(q + q') x + x' = 1

x.1=x

Repeated terms are considered once.

=

$$pqr + pqr' + pqr + pqr + p'qr + pqr + pqr' + pqr' + pqr' + pq'r$$

=  $pqr + pqr' + p'qr + pq'r$

=  $p'qr + pq'r + pqr' + pqr$

=  $m_3 + m_5 + m_6 + m_7 = \sum m (3, 5, 6, 7)$

#### ii) Product of Maxterms

$$F(p, q, r) = (pq + r) (q + pr)$$

$$= (p + r) (q + r) (q + p) (q + r)$$

$$= (p + r) (q + r) (q + p)$$

$$= (p + r + (qq')) ((pp') + q + r) (p + q + (rr'))$$

$$= (p + r + q) (p + r + q') (p + q + r) (p' + q + r) (p + q + r') (p + q + r')$$

$$= (p + q + r) (p + r + q') (p' + q + r) (p + q + r')$$

$$= (p + q + r) (p + q + r') (p + q + r') (p' + q + r)$$

$$= M. M. M. M. = \Pi M (0, 1, 2, 4)$$

#### Example 1.14

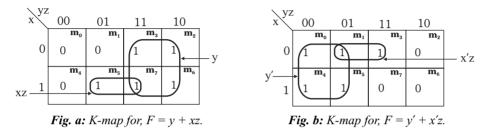

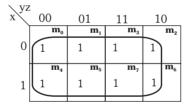

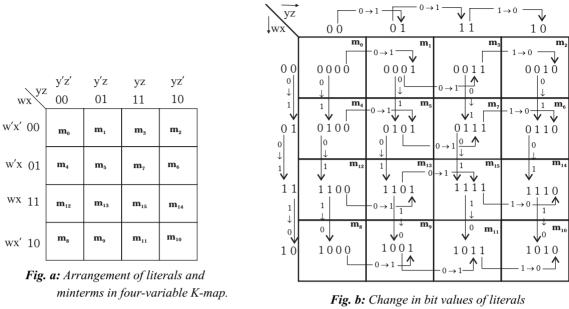

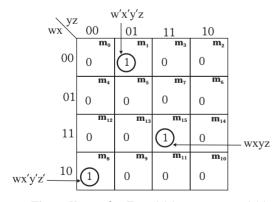

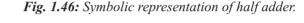

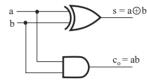

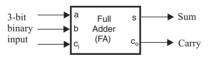

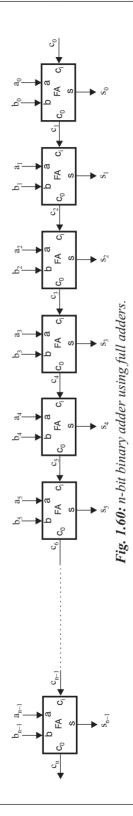

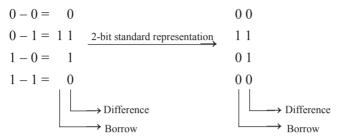

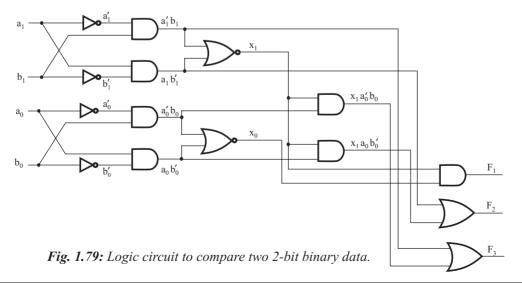

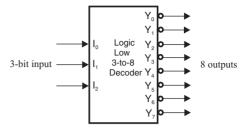

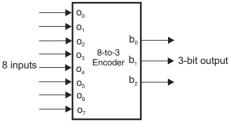

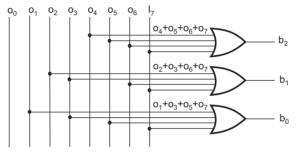

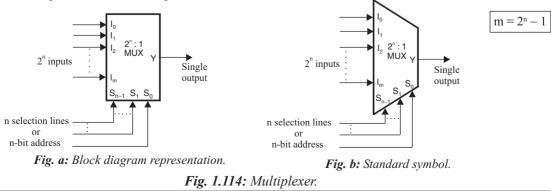

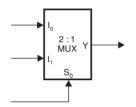

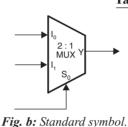

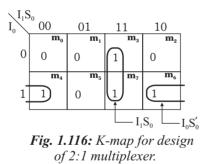

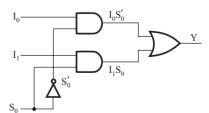

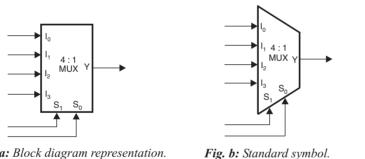

Convert the following in the proper canonical form and write the decimal notation.